Contents list available at CBIORE journal website

## Remarkable Energy Development

Journal homepage: https://ijred.cbiore.id

Research Article

## The implementation of ozone cleaning on two-step texturization of ptype silicon wafer

Mohd Norizam Md Daud<sup>a\*</sup>, Amin Aadenan<sup>a</sup>, Lim Chin Haw<sup>a</sup>, Najah Syahirah Mohd Nor<sup>b</sup>, Mohd Adib Ibrahim<sup>a</sup>, Mohd Asri Mat Teridi<sup>a</sup>

<sup>a</sup>Advanced Solar Cell Fabrication Laboratory, Solar Energy Research Institute, Universiti Kebangsaan Malaysia, 43600 Bangi, Selangor, Malaysia <sup>b</sup>Malaysian Meteorological Department, Jalan Sultan. 46667 Petaling Java, Selangor, Malaysia

**Abstract**. This study investigates the ozone treatment process that can be utilized across various fabrication stages to enhance the performance of silicon solar cells. The effectiveness of this treatment on p-type silicon surfaces was examined through the application of ozone dissolved in deionized water (DIO<sub>3</sub>) and the ultraviolet-ozone (UVO<sub>3</sub>) cleaning process prior to the two-step texturization procedure. The two-step texturization procedure applied in this work eliminates the use of silicon nitride (SiN) as an anti-reflective coating (ARC) layer for the elimination of toxic gases and leads to the environment-friendly fabrication of solar cells. An alternative to RCA, DIO<sub>3</sub> and UVO<sub>3</sub> represent promising chemical options for cleaning applications to eliminate the use of hazardous chemicals. It was discovered that the surface with the DIO<sub>3</sub> treatment for 10 minutes resulted in a significantly enhanced surface quality on the p-type silicon wafer. In the DIO<sub>3</sub> cleaning, ozone is dissolved in deionized water to create a highly oxidative solution capable of removing organic contaminants and particles effectively. In contrast, the UVO<sub>3</sub> treatment harnesses ultraviolet light to synthesize ozone directly on the wafer's surface, promoting the degradation of organic residues into volatile compounds, including CO<sub>2</sub> and H<sub>2</sub>O. According to field emission scanning electron microscope (FESEM) micrographs and UV-visible spectrometer (UV-Vis) measurements, the textured wafer with DIO<sub>3</sub> treatment improves the surface morphology and decreases the front surface reflection. As a result, the 10 minutes DIO<sub>3</sub> treatments were reported optimal; the range size and height of the pyramid formed were 1.9–2.0 µm and 0.8–1.5 µm, offering a lower reflectivity value of below 12%, respectively. Results from the Atomic Force Microscope (AFM) also confirm that the increase in average surface roughness from 203.65 nm to 300.27 nm was expected to improve light absorption. Moreover, this methodology leads to a considerable reduction i

Keywords: DIO₃ treatment, two-step texturization, p-type wafer, surface morphology, reflectance

@ The author(s). Published by CBIORE. This is an open access article under the CC BY-SA license (http://creativecommons.org/licenses/by-sa/4.0/).

Received: 7th Nov 2024; Revised: 6th January 2025; Accepted: 25th January 2025; Available online: 7th Feb 2025

## 1. Introduction

The efficiency of a solar cell is a crucial attribute, as it directly influences the cell's ability to produce electrical power. Therefore, there is a significant demand for techniques that not only increase the efficiency of solar cells but also refine the manufacturing processes associated with their production (Oni et al., 2024). The modification of the pre-texturization process not only prepares the silicon wafer for efficient texturization but also improves the overall manufacturing process by enhancing surface cleanliness, morphology, and hydrophilicity while environmental impact. These improvements collectively lead to higher-quality solar cells with improved performance and manufacturing efficiency. The modification of the pre-texturization process on the silicon (Si) wafer presented in this study specifically improves surface properties such as reduced surface roughness and enhanced uniformity, which contribute to better light trapping and minimized carrier recombination. Additionally, optical properties such as increased reflectance reduction and optimized light absorption

are achieved, thereby improving the overall manufacturing process and performance of Si solar cell architectures.

The pursuit of developing solar cells with enhanced efficiency, simplified manufacturing processes, and reduced costs is an ongoing endeavor (Panagoda et al., 2023). Achieving this objective requires optimizing every step of the production process. Surface cleaning plays a pivotal role in device performance. Thorough cleaning is essential for eliminating dust, contaminants, particles, organic and inorganic impurities, and native oxides from the wafer surface, which ensures optimal device functionality. A variety of cleaning methods are available, broadly categorized into wet chemicals (C. L. Chu et al., 2020; Kart et al., 2018) and dry-cleaning techniques (Neutens et al., 2018). Wet chemical cleaning has been the cornerstone of wafer preparation for decades, with the Radio Corporation of America (RCA) clean recognized as the principal method in the microelectronics sector (Kern & Puotinen, 1970; Ruzyllo et al., 1990). This technique, while highly effective, involves the use of multiple hazardous chemicals such as NH<sub>4</sub>OH and H<sub>2</sub>O<sub>2</sub>. To address environmental and economic concerns, alternatives such as IMEC-Clean have been introduced, which optimize

chemical usage while maintaining high cleaning efficiency (W. Chen et al., 1997). Among wet chemical methods, DIO<sub>3</sub> has gained prominence due to its strong oxidizing properties and ease of generation through dielectric barrier discharge (G. Chen, 1999; Moldovan et al., 2013; Zou et al., 2021). Studies have highlighted its effectiveness in removing contaminants and preparing wafer surfaces for subsequent processing (Epelle et al., 2023). However, despite the proven advantages of wet cleaning methods, their reliance on large volumes of chemicals and water raises concerns about sustainability and compatibility with next-generation manufacturing technologies. To overcome these limitations, dry cleaning techniques have emerged as complementary or alternative methods. One notable approach is the UVO<sub>3</sub> process. The UVO<sub>3</sub> method combines UV radiation with molecular oxygen to produce reactive species such as ozone (O<sub>3</sub>) and atomic oxygen. These species oxidize and decompose organic residues into volatile byproducts like CO<sub>2</sub> and H<sub>2</sub>O, effectively removing contaminants without the use of liquid chemicals. The term photosensitized oxidation describes the chemical reactions initiated by UV radiation in the presence of oxygen, leading to the formation of highly reactive species such as singlet oxygen and ozone. These species facilitate efficient cleaning, making the UVO<sub>3</sub> process an environmentally friendly and effective solution. First reported by Bolon and Kunz in 1972, the UVO<sub>3</sub> process has since been demonstrated to improve wafer surface morphology, enhance transmittance, and promote the overall quality of films in applications such as organic photovoltaics (Bolon & Kunz, 1972; Li et al., 2023). By integrating both wet and dry-cleaning techniques into a unified cleaning strategy, it is possible to harness their respective advantages, addressing both the environmental technological demands of modern silicon wafer processing.

Various texturing techniques have been developed to create pyramid-like structures on Si wafers, each with distinct mechanisms and implications for surface morphology and optical properties. For example, electrochemical etching relies on applying an electrical current to selectively remove silicon, offering precise control over texture but requiring complex setups and stringent conditions (Menna et al., 1995). Metalassisted chemical etching (MACE) involves the use of metal catalysts to enhance Si dissolution, allowing the formation of high-aspect-ratio structures. However, its dependence on hazardous chemicals can pose environmental and handling challenges (Fang et al., 2008). Physical dry etching, such as plasma etching, physically removes material through ion bombardment, enabling fine control over texture but often at the expense of slower processing rates and higher costs (Garnett & Yang, 2010). The discussion from general texturing methods to those used in industrial applications is important to consider scalability and cost-effectiveness. In the context of industrial-scale solar cell manufacturing, texturization methods primarily employ chemical etching due to their scalability and cost-effectiveness. Conventional methodologies typically utilize alkaline etching solutions, such as isopropyl alcohol (IPA), potassium hydroxide (KOH), and deionized water (DI), to create pyramid-like structures on the Si surface (Chuchvaga et al., 2020; Montesdeoca-Santana. et al., 2013). These solutions exploit the anisotropic etching properties of Si, preferentially dissolving certain crystallographic planes to form pyramids. The outcomes of these industrial processes are strongly influenced by the underlying texturing parameters. Under standard conditions, the resulting pyramid sizes are approximately 2 µm (Jiang et al., 2015). However, variations in process parameters, etching time, temperature, and concentration, can yield pyramid sizes ranging from 2 µm to 8 µm. This is with corresponding reflectivity values between 14% and 15%. The structured surface produced by pyramid texturing enhances light absorption through numerous internal reflections, reducing reflectivity by approximately 20% compared to flat surfaces. This reduction in reflectivity, along with improvements in carrier lifetime, is closely tied to the size, distribution, and uniformity of the pyramids (Ju *et al.*, 2016). Thus, the transition from general texturing methods to industrial processes emphasizes the need for balancing scalability, environmental considerations, and the optimization of pyramid-textured surfaces to improve solar cell performance.

This study investigates the application of cleaning techniques using DIO<sub>3</sub> and UVO<sub>3</sub>, newly integrated with a twostep texturing method, to improve the textural properties of Si wafers while reducing costs, processing time, and chemical usage. The two-step texturing procedure begins with 60 cyclic voltammetry (CV) cycles, a technique involving repeated cycling of the electrode potential to promote controlled surface modification. These cycles assist in forming an initial nanotextured surface by selectively removing material and enhancing the silicon's readiness for the subsequent alkaline etching process. This is followed by a standard alkaline texturing step utilizing KOH and IPA, which generates microscale pyramidal structures to enhance light trapping. As detailed in prior research (Norizam et al., 2024), the optimized process effectively combines nano- and micro-scale texturing to achieve superior light absorption characteristics. In this study, five cleaning durations for both DIO3 and UVO3 treatments were tested to identify the optimal conditions for texturization. The results demonstrated that ozone-based cleaning not only enhanced the efficiency of the texturing process but also led to a significant reduction in reflectance. The baseline reflectance of the p-type Si wafer was approximately 30%, and the DIO<sub>3</sub> and UVO<sub>3</sub> treatments reduced reflectance by 40-45% relative to the baseline value, achieving reflectance values as low as 16-18%. Moreover, the ozone-based cleaning and texturing approach emphasizes cost-effectiveness. It also reduces chemical consumption by minimizing the need for additional cleaning agents while also shortening processing times compared to conventional methods.

#### 2. Method

#### 2.1 Cleaning and texturization of p-type silicon wafers

A p-type monocrystalline Si wafer, sourced from Nexolon Company, was utilized in this study. The wafer exhibits a thickness of approximately 200 µm and a resistivity ranging from 0.5 to 3.0  $\Omega$ cm. The wafers, measuring 20 mm  $\times$  20 mm, were subjected to advanced cleaning processes DIO<sub>3</sub> and UVO<sub>3</sub> with the primary objective of optimizing surface preparation for subsequent texturization. By removing organic and inorganic contaminants, native oxides, and particles, these cleaning methods aim to improve the uniformity and quality of the textured surface, ultimately enhancing the optical and electrical performance of the wafers. For the UVO<sub>3</sub> cleaning procedure, a Jelight 42 UV-ozone generator was employed to produce ozone and generate oxide on the wafer surface. The samples were exposed to the generator for intervals of 5, 10, 15, 20, and 25 minutes on each side. The samples were then immersed in a 5% acid hydrofluoric (HF) solution by volume to remove the oxide layer formed during the UVO<sub>3</sub> process. In the DIO<sub>3</sub> cleaning procedure, the samples were immersed in deionized water (BiOLUX Hydrogen Fountain) containing dissolved ozone at a concentration of approximately 4.0 ppm, maintained at ambient temperature. The immersion durations were also set to 5, 10,

15, 20, and 25 minutes, followed by rinsing in deionized water for 1 minute and drying using a nitrogen ( $N_2$ )-based dryer.

Following the completion of the cleaning procedure, the texturing process was executed using CV treatment, followed by the application of an alkaline solution. The CV treatment was conducted utilizing an Autolab potentiostat/galvanostat (Metrohm, Model: PGSTAT 204) integrated into a threeelectrode electrochemical setup. In this configuration, the Si sample acted as the working electrode, platinum served as the counter electrode, and a standard Ag/AgCl (3M KCl) electrode was used as the reference electrode. The choice of a 0.5M Na<sub>2</sub>SO<sub>4</sub> electrolyte at approximately pH ~7 was based on its stability, non-reactivity with the Si substrate, and ability to support consistent electrochemical cycling. The potential range of -1.0 to 1.0 V (vs. Ag/AgCl) and the sweep rate of 0.1 V/s were selected to balance the uniformity of surface modification and process duration, as reported in prior studies (Norizam et al., 2024). A total of 60 voltammetric cycles were performed, as this number was optimized based on a combination of surface morphology, reflectivity, and carrier lifetime results in earlier research. The alkaline texturing process involved mixing KOH, IPA, and DI water in a ratio of 1:5:125. This specific ratio was selected since it promotes the formation of uniform micro-sized pyramidal structures by balancing the etching rate and maintaining surface wettability. The reaction temperature was maintained at 70°C, ensuring a consistent etching process without inducing excessive surface roughness. The reaction duration was set to 30 minutes to achieve optimal pyramid formation while minimizing over-etching or material degradation. The resultant surface texturing significantly enhances light absorption due to the reduction in reflectivity caused by the micro-pyramids.

# 2.2 Morphological and optical properties characterization of p-type silicon wafers

The morphology of the textured samples was examined utilizing FESEM with a Zeiss SUPRA 55 VP instrument. Additionally, FESEM was employed post-texturing to analyze the cross-sectional images and to quantify the height and average dimensions of the pyramidal structures resulting from various cleaning duration followed by the two-steps texturization process. The topographic images obtained through AFM were captured in tapping mode utilizing the AFM Nanosurf Easyscan 2. This system is an atomic force microscope capable of measuring the topography of samples along with various other properties at a resolution on the nanometer scale. The surface reflectance of each sample was examined using a UV-Visible Spectrometer (Model: LAMBDA 35) in the wavelength spectrum of 400-700 nm. Subsequently, structural characterization was performed using an X-Ray Diffractometer (XRD) (Bruker, D8 Advance).

#### 3. Results and discussion

## 3.1 Surface roughness analysis

The process of surface cleaning aims to eliminate all forms of dust, contaminants, particles, and both organic and inorganic impurities, as well as native oxides from the wafer surface. This procedure is critical for device performance, as thorough cleaning ensures optimal quality and functionality. To assess the impact of ozone treatment and subsequent cleaning procedures, AFM analysis was conducted to evaluate key surface characteristics, including surface roughness, morphology, and

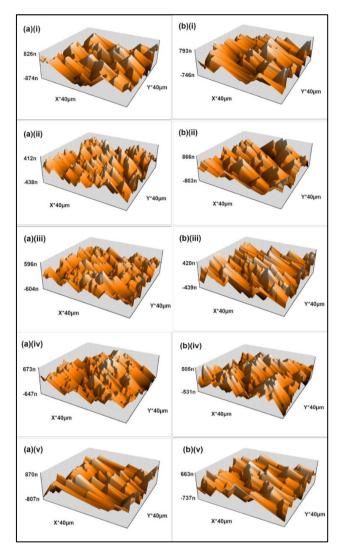

**Fig 1.** AFM images of (a) DIO<sub>3</sub> and (b) UVO<sub>3</sub> cleaning process for (i) 5, (ii) 10, (iii) 15, (iv) 20 and (v) 25 minutes exposure time

potential residual contamination levels on the Si wafer. The AFM images were recorded following the two-step texturing procedure, providing detailed insights into the nanoscale surface structure and uniformity of the wafer. A clean wafer surface plays a pivotal role in enhancing the effectiveness of the texturing process. By removing impurities and ensuring a uniformly smooth surface, the interaction between the wafer and the texturing solution becomes more predictable, leading to more uniform and well-defined texturing patterns. This improvement is expected to result in reduced reflectivity, better light trapping capabilities, and increased carrier lifetime, all of which contribute to the overall performance and efficiency of the Si wafer in solar cell applications.

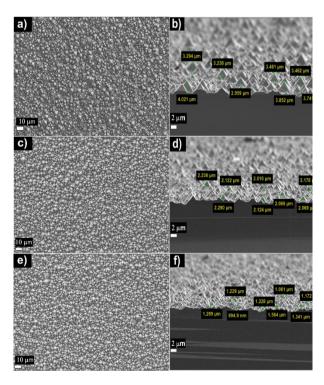

Fig 1 (a) and (b) display the AFM images of  $DIO_3$  and  $UVO_3$  treatments across five distinct exposure durations, respectively. The AFM images illustrate that the application of ozone cleaning prior to the texturing process results in optimal surface roughness, which is essential for the effective performance of solar cells. The  $DIO_3$  cleaning process, characterized by a 10-minutes immersion period, results in a superior rough surface, as illustrated in Fig 1 (a)(ii). In contrast, the  $UVO_3$  exposure requires a longer duration, as displayed in Fig 1 (b)(iv), to achieve an optimized rough surface that minimizes reflection effectively.

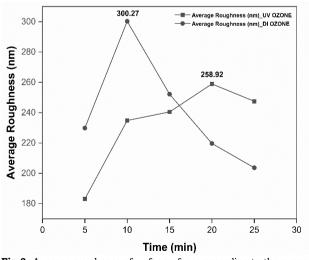

Fig 2 illustrates the changes in the average roughness of the Si surface in relation to the exposure to UVO $_3$  and DIO $_3$ , as well as the duration of immersion. The optimal average roughness of 300.27 nm was attained after a 10-minutes immersion in DIO $_3$ . The data presented in Fig 2 indicate that following immersion treatment in DIO $_3$  for durations of 15, 20, and 25 minutes, the average roughness values decrease to 252.19 nm, 219.68 nm, and 203.65 nm, respectively. The data indicate that the rate of decrease in average roughness is more pronounced during the 15–25-minutes interval when compared to the period prior to 10 minutes.

Consequently, the efficiency of contaminant removal is significantly higher in the initial 10 minutes than in the subsequent time frame. The UVO<sub>3</sub> treatment illustrated in Fig 2 indicates that the optimal average roughness is attained after an exposure duration of 20 minutes. The average roughness for exposure of 5, 10, and 15 minutes was 183.11 nm, 234.83 nm and 240.49 nm, respectively. Subsequent exposure beyond the 20-minutes mark results in a decrease in average roughness (247.51 nm) compared to the measurements taken prior to this time interval. As a result, it can be inferred that the UVO<sub>3</sub> treatment represents a more time-intensive cleaning procedure for applications involving solar cells.

Both UVO<sub>3</sub> and DIO<sub>3</sub> treatments result in the formation of a thin Si oxide layer on the Si surface. This oxide layer serves to passivate the surface, thereby diminishing recombination sites, which is beneficial for solar cell performance (M. Chu *et al.*, 2024). In the initial phases of UVO<sub>3</sub> or DIO<sub>3</sub> treatment, the growth of the oxide can induce localized discrepancies in surface morphology. Such roughness may arise from varying oxidation rates across the Si surface, often influenced by inherent defects or the initial atomic-scale roughness. During the early treatment stages, the oxidation process occurs relatively rapidly, leading to an increase in surface roughness due to the non-uniform formation of the oxide layer (Jun *et al.*, 1995). This roughness is attributed to the uneven oxide development across different crystal orientations or microstructural features present on the Si surface.

After a certain period, the oxidation rate diminishes as the oxide layer becomes thicker. This reduction is primarily attributed to the diffusion-limited nature of the oxidation process, where oxygen molecules or oxidizing species must diffuse through the already-formed oxide layer to reach the underlying substrate. As the oxide layer grows, the diffusion pathway lengthens, reducing the rate at which oxidation occurs.

${\bf Fig~2.}$  Average roughness of wafer surfaces according to the ozone treatment

This self-limiting behavior results in a more uniform surface as the oxidation process stabilizes and progresses consistently across the substrate. Thickness variations in the oxide layer can initially lead to non-uniform growth rates. However, over time, the process inherently compensates for these irregularities as thicker regions experience slower oxidation due to the extended diffusion path, while thinner regions oxidize more rapidly. This dynamic contributes to surface smoothing by gradually covering the initial irregularities and creating a consistent oxide layer across the substrate.

Prolonged or excessive exposure to ozone treatment may result in surface oxidation, roughening, and possible structural impairment of the Si wafer, which could be potentially harmful, depending on the application (Bakhshi et al., 2018). Moreover, prolonged exposure can result in excessive oxidation, forming a thicker-than-desired silicon oxide layer (Özçam et al., 2014). With prolonged treatment durations, the oxide layer becomes more uniform as it consistently covers both high and low areas on the surface. This "filling in" contributes to a decrease in the overall surface roughness. Initially, treatments with UVO3 or DIO<sub>3</sub> result in an increase in the roughness of the Si surface due to rapid and non-uniform oxidation. However, as the oxide layer continues to thicken and attain a more uniform structure, the surface ultimately becomes smoother, achieving a stable and self-limiting thickness refers to the point at which the growth rate of the oxide layer significantly slows down due to the diffusion-limited nature of the oxidation process (Fu et al., 2024). Therefore, managing the duration of ozone exposure is crucial for maximizing beneficial outcomes while minimizing potential negative effects.

#### 3.2 X-ray diffraction analysis

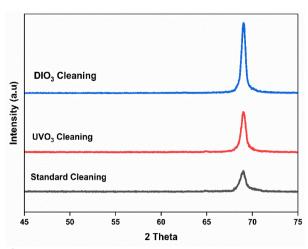

The XRD analysis was conducted to determine the crystallinity of the samples, focusing on the structural integrity of the Si wafers after different cleaning processes. The analysis demonstrates a prominent peak centered at 69.1° (JCPDS file 271402), corresponding to the (400) plane of Si, which is a key indicator of silicon's crystalline structure. Fig 3 illustrates the XRD patterns for Si wafers subjected to various cleaning treatments, highlighting significant differences in crystallinity. Among the treatments, the DIO<sub>3</sub> cleaning process exhibits the highest peak intensity, indicating enhanced crystallinity compared to the other methods. The enhancement in crystallinity observed with DIO<sub>3</sub> cleaning could be attributed to its effective removal of surface contaminants and oxides, ensuring a pristine and smooth Si surface. By eliminating impurities and native oxide layers more efficiently than other methods, DIO<sub>3</sub> cleaning minimizes surface defects that could otherwise disrupt the alignment of Si atoms. This results in a more orderly and well-defined crystal lattice, which is crucial for semiconductor applications. Fig 3 specifically underscores the correlation between cleaning methods and the structural quality of the Si wafers, with DIO<sub>3</sub>-treated wafers demonstrating superior crystallinity as evidenced by the intensity and sharpness of the (400) peak.

The ozone treatments primarily affect only the very top surface layer of the Si wafer by forming a thin Si oxide layer, typically a few nanometers thick. This oxidation process is considered mild since it is performed at ambient temperature, without the involvement of high temperatures, harsh chemicals, or physical abrasion, and relies solely on the reactive species generated by ozone (Fink *et al.*, 2009). Since the implemented ozone treatment does not involve high temperatures or physical abrasion, the underlying crystal structure of the silicon remains mostly unaffected. It refers to a negligible structural impact on

Fig 3. XRD patterns of the different cleaning process of silicon wafer for standard cleaning, 20-min  $UVO_3$  and 10-min  $DIO_3$

the underlying crystal lattice of the silicon. While the surface undergoes oxidation, the bulk silicon retains its original crystalline structure, as the ozone treatment does not introduce thermal stress or induce significant changes beyond the surface oxide formation. This ensures that the intrinsic properties of the silicon wafer remain intact, preserving its suitability for high-precision applications. Moreover, the amorphous nature of the oxide layer ensures compatibility with subsequent processing steps, as it forms a uniform and defect-free barrier.

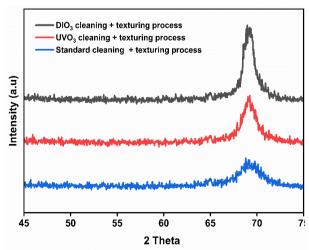

The XRD pattern presented in Fig 4 reveals that the peak intensity increases when two-step textured wafers are subjected to the DIO<sub>3</sub> cleaning process. This enhancement in intensity suggests that DIO<sub>3</sub> cleaning contributes to higher crystallinity by removing surface contaminants and native oxides more effectively, thereby exposing and preserving the intrinsic crystalline structure of the Si substrate. In contrast, the samples cleaned using standard cleaning and UVO3 methods exhibit a reduction in XRD intensity. This reduction may be attributed to less effective cleaning, which leaves residual contamination or uneven oxide layers that interfere with the structural regularity of the Si surface. The correlation between surface morphology and crystallinity is further supported by the analysis of Fig 8(e), which displays the surface morphology of the samples. The smoother and more uniform surface observed in the DIO3 cleaned wafers aligns with the higher XRD intensity, as a welltextured, clean surface minimizes scattering and enhances the detection of crystalline planes. Conversely, the less uniform and rougher morphology of the UVO<sub>3</sub> and standard-cleaned wafers contributes to reduced crystallinity, as these surfaces are more prone to structural distortions and defects that degrade crystalline order.

Texturing is a more aggressive process designed to create a textured pyramid pattern on the Si surface. This process involves anisotropic etching, which preferentially removes material along specific crystal planes of silicon, typically the (111) plane, due to differences in etching rates among crystal orientations (Akila *et al.*, 2017). The result is the formation of well-defined facets with specific orientations, which enhances light trapping and reduces surface reflectivity. Ozone treatment, on the other hand, affects only the very top surface by forming a thin amorphous Si oxide layer without significantly altering the crystallinity of the Si wafer. The two-step texturing process combines the benefits of light-trapping textures from etching

with the preservation of the bulk silicon's crystalline structure, ensuring that the material retains its essential properties for efficient solar cell performance.

In both the ozone and texturing processes, the bulk crystallinity of the Si wafer remains intact, which is crucial for maintaining the electrical properties required for efficient solar cell operation. Bulk crystallinity ensures the Si crystal lattice is well-ordered and free of significant defects, directly impacting charge carrier mobility. High-quality crystalline Si allows for minimal scattering and recombination of charge carriers (electrons and holes), enabling them to travel efficiently through the material to the electrodes. This high carrier mobility translates to better current flow and higher conversion efficiency in solar cells. Any disruption to the bulk crystallinity, such as the introduction of defects or amorphous regions, would result in increased recombination rates, reducing the overall performance of the solar cell.

Tables 1 and 2 provide the full width at half-maxima (FWHM), crystallite size and peak positions for various cleaning and texturization processes. FWHM refers to the width of a peak at its half-maximum intensity in an X-ray diffraction (XRD) pattern. It is a measure used to estimate the crystallite size and lattice strain in materials. A narrower FWHM corresponds to larger crystallite sizes and lower lattice strain, indicating higher crystal quality. FWHM analysis to estimate the crystallite size and detect strain in a material. Remarkably, the texturing with 10 minutes DIO<sub>3</sub> cleaning suggests that the FWHM does not demonstrate substantial changes, which suggests that the crystallite size is effectively constant. The size of the crystallites within a Si wafer can substantially impact its optical characteristics, particularly in light reflectance. Smaller crystallites introduce more grain boundaries, which can scatter light more effectively, increasing light absorption in textured surfaces. The anticipated crystallite sizes of the samples were consistently 80 nm across all samples, regardless of the texturing observed. This size provides a balance small enough to enhance surface interaction with light yet large enough to maintain structural stability and minimize excessive grain boundary effects. This value lies within the medium crystallite size range (10 nm - 100 nm), where there can be noticeable changes in reflectance, and the optical properties start to stabilize compared to smaller sizes (<10 nm) (Das & Sarkar, 2016).

These smaller crystallite sizes generally increase surface roughness due to more grain boundaries and irregularities,

Fig 4. XRD patterns of the after-two-step texturing process of silicon wafer

Data obtained from XRD patterns for different cleaning process

| Camania.                  | FWHM      | Crystallite | Peak Position |

|---------------------------|-----------|-------------|---------------|

| Sample                    | (2 Theta) | Size (nm)   | (2 Theta)     |

| Standard cleaning         | 0.81      | 80.66       | 69.17         |

| UVO₃ cleaning             | 0.65      | 142.51      | 69.17         |

| DIO <sub>3</sub> cleaning | 0.53      | 169.68      | 69.17         |

Table 2

Data obtained from XRD patterns after texturing process

| Sample                      | FWHM<br>(2 Theta) | Crystallite<br>Size (nm) | Peak Position<br>(2 Theta) |

|-----------------------------|-------------------|--------------------------|----------------------------|

| Standard cleaning +         | 1.25              | 78.41                    | 69.17                      |

| Texturing process           | 1.25              | 70.41                    | 09.17                      |

| UVO <sub>3</sub> cleaning + | 1.00              | 77.00                    | 60.17                      |

| Texturing process           | 1.29              | 77.83                    | 69.17                      |

| DIO <sub>3</sub> cleaning + | 1.00              | 70.00                    | 60.17                      |

| Texturing process           | 1.32              | 76.09                    | 69.17                      |

especially in crystalline Si (Khanna *et al.*, 2015). For solar cell applications, achieving an optimal pyramid size and roughness is key to balancing light trapping (Park et al., 2020).

The data presented in Section 3.2 reveal that the DIO<sub>3</sub>-treated wafers achieved a consistent crystallite size of approximately 80 nm across different texturing durations, with minimal changes in FWHM. This result indicates that the treatment maintains the structural integrity of the Si surface while allowing for effective texturing. The textured surfaces demonstrated uniform pyramid structures with dimensions conducive to effective light trapping. Moreover, the roughness introduced by the texturing process aligns well with the medium crystallite size, ensuring reduced reflectance and enhanced absorption. The balance between surface roughness and crystallite size achieved through the DIO<sub>3</sub> process is a key outcome. This is attributed to the fact that it supports the creation of efficient light-trapping structures while preserving

the electrical properties of the underlying silicon. This highlights the effectiveness of DIO<sub>3</sub> cleaning in maintaining an optimal surface morphology for solar cell performance.

#### 3.3 Spectral reflectance analysis

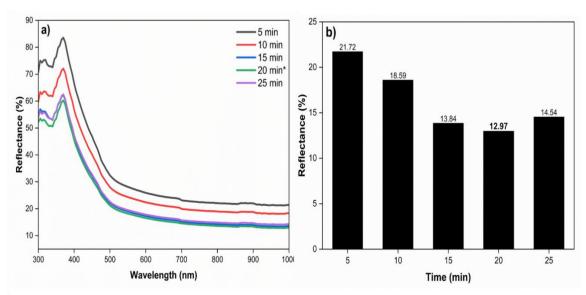

The enhancement of minority carrier lifetime and photoelectric conversion efficiency in monocrystalline Si solar cells is notably achieved through the reduction of optical reflectance, which allows for the capture of increased incoming light (Kegel  $et\ al.$ , 2013). The reflectance data depicted in Fig 5 corresponds to the variations in UVO3 cleaning time. Optical reflectance for the wafers diminishes with increasing wavelength up to 600 nm while maintaining relative constancy between 600 and 1000 nm, as displayed in Fig 5 (a). The wafers treated with 20 minutes of UVO3 demonstrate the lowest

Fig 5. (a) Reflectance spectrum of UVO3 samples and (b) minimum percentage of reflectance values with different time of UVO3 cleaning process

Fig 6. (a) Reflectance spectrum of DIO<sub>3</sub> samples and (b) minimum percentage of reflectance values with different time of DIO<sub>3</sub> cleaning process

reflectance (12.97%), which is in good agreement with the large surface roughness of the samples.

The presence of significant surface roughness can enhance the light-trapping capabilities of the textured surface (Fashina et al., 2018). Despite that, the reflectance of wafers starts to increase after being subjected to 25 minutes, where the wafers exhibit a reflectivity of 14.54%. The analysis of AFM images for samples subjected to 5 minutes of UVO<sub>3</sub> treatment Fig 1 (b)(i) reveals significant non-etched regions and a relatively low surface roughness on the wafer's surface, which diminishes the wafers' capacity for effective light trapping. Fig 5(a) illustrates the AFM image of a wafer subjected to 5 minutes of UVO<sub>3</sub> treatment. The image highlights a surface characterized by significant non-etched regions with a relatively low surface roughness. The surface appears smoother, with fewer pronounced peaks and valleys compared to samples subjected to longer treatment times. This lack of surface texturing reduces the wafer's ability to trap light effectively, thereby diminishing its optical performance. The comparison between Fig 5(a) and other AFM images emphasizes the importance of achieving adequate surface roughness through optimized treatment durations. Insufficient etching, as observed here, can lead to higher reflectivity and lower light absorption, which are detrimental to the performance of solar cells.

Fig 6 indicates the reflectance measurement of Si wafers textured by different  $DIO_3$  time processes as a function of wavelength. According to Fig 6 (b), the wafers subjected to the two-step texturing process with 10 minutes of  $DIO_3$  cleaning treatment demonstrate the smallest surface reflectance (11.57%) compared to other time processing. The results demonstrate that superior anti-reflection properties are attained by utilizing small pyramid dimensions, ensuring effective surface coverage, and maintaining a uniform and homogeneous arrangement of the pyramids, as depicted in Fig 8 (e) (Al-Husseini & Lahlouh, 2019).

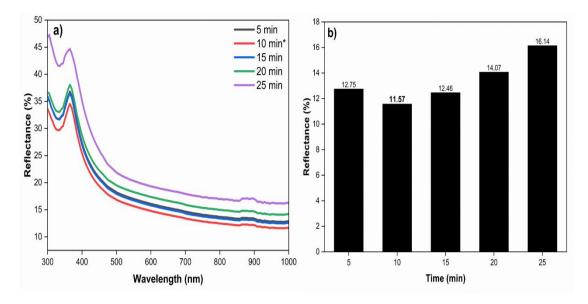

The correlation between the surface roughness and the reflectance of each wafer is presented in Fig 7. The two-step texturing process with 10 minutes of  $DIO_3$  cleaning time yields wafers with the highest value of average roughness (300.27 nm)

**Fig 7.** Average roughness and reflectance of wafer surfaces according to the cleaning process

and the lowest reflectance value (11.57%). The result is anticipated to enhance the efficacy of solar cells.

The presence of significant surface roughness can enhance the light-trapping capabilities of the textured surface (Fashina et al., 2018). However, the reflectance of wafers increases after 25 minutes of treatment, reaching a reflectivity of 14.54%. The analysis of AFM images for samples subjected to 5 minutes of UVO<sub>3</sub> treatment reveals significant non-etched regions and relatively low surface roughness on the wafer's surface, which diminishes the wafers' capacity for effective light trapping. Fig 7 illustrates the relationship between the surface roughness and the reflectance of each wafer. The two-step texturing process with 10 minutes of DIO<sub>3</sub> cleaning time yields a wafer with the highest value of average roughness (300.27 nm) and the lowest reflectance value (11.57%). The result is anticipated to enhance the efficacy of solar cells.

## 3.4 Microstructure on different textured wafers

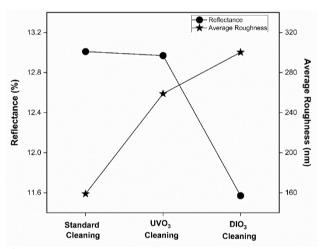

Fig 8 (a, c and e) presents the FESEM images of textured Si wafer surfaces subjected to different cleaning methods. Fig 8 (b, d and f) represents pyramid facets obtained from the cross-section of the samples. In general, a random pyramidal structure was successfully developed on all samples, signifying the ability of each approach to be employed as a cleaning method. This micrograph indicates that the ozone-cleaning process can significantly enhance the texturing process for Si wafers by modifying the surface properties (Gao, 2021). During the texturing process, the Si wafer is often treated to create a pyramidal structure that increases light absorption (Zhang *et al.*, 2021).

The ozone cleaning procedure does not directly influence the dimensions of the pyramids formed on a Si wafer. Instead, it serves to maintain a clean and uniform surface on the Si wafer, eliminating organic contaminants and particles that may lead to irregular texturing. A uniform surface is essential for ensuring uniform pyramid dimensions throughout the wafer, as any contamination may lead to defects or discrepancies in the size of the pyramids. The size of the pyramids is predominantly influenced by the texturing process, which is contingent upon the crystal orientation of the Si wafer. In this study, the texturing process has been refined based on previously reported findings (K & O, 2023; Raji *et al.*, 2022).

Following the texturing process, the intercept method was employed to determine the size of the pyramid (Park et al., 2009). The intercept method is to draw diagonal lines on the FESEM image and count the number of diagonal pyramids. The number of pyramids intersecting the line is counted. The average pyramids are determined by dividing the number of intersections by the actual line length.

As a result of the measurement, the pyramid size of the textured sample with standard cleaning is  $4.3-4.6 \mu m$ ,  $UVO_3$

**Fig 8.** FESEM micrographs of Si surface and variation of pyramid height after textured for different cleaning process: (a & b) standard cleaning, (c & d) UVO<sub>3</sub> cleaning and (e & f) DIO<sub>3</sub> cleaning

cleaning 3.2–3.3 µm, and DIO $_3$  cleaning 1.9–2.0 µm. The findings after ozone cleaning distinctly indicate that the surface condition prior to texturing influences the development of the pyramid structure. Furthermore, following the DIO $_3$  cleaning process, a more consistent pyramid shape can be observed. As depicted in Fig 8 (b, d, and f), the pyramidal development resulting from the DIO $_3$  cleaning process is considerably more substantial than the standard and UVO $_3$  process. Furthermore, the size of the pyramids generated through DIO $_3$  is the smallest when compared to the other cleaning processes.

Ultimately, the adoption of  $DIO_3$  treatment plays a crucial role in improving the efficiency of textured Si wafer manufacturing by facilitating comprehensive cleaning and oxidation and ensuring uniformity in the etching process. This process ultimately results in the attainment of the desired pyramid size, thereby enhancing performance while reducing the time required for cleaning. Compared to the traditional RCA washing method,  $DIO_3$  uses fewer chemicals while delivering superior results. Additionally, the  $DIO_3$  process reduces chemical usage costs and improves the performance of solar cells, making it a more efficient and cost-effective solution.

#### 4 Conclusion

This study has effectively demonstrated a viable cleaning method for texturizing the surfaces of p-type Si wafers through a two-step texturing procedure. The DIO $_3$  cleaning process results in the formation of pyramidal structures of varying sizes, enhancing the efficacy of surface texturization. A 10-minutes DIO $_3$  cleaning process obtained a good time for creating the surface with a homogenous and uniform pyramidal size, where the lowest surface reflectance was discovered at 11.57%. The average pyramid size and height were 1.9  $\mu m$  and 1.2  $\mu m$ , respectively. Therefore, the implementation of the DIO $_3$  cleaning process, as detailed in this research, presents a viable approach for developing a simple, cost-effective, and non-toxic solar cell that exhibits improved conversion efficiency.

## Acknowledgments

We would like to thank Mr. Mohamad Arif Mokhtar, Mr. Amirul Iman Zainudin, Mr. Raja Mohd Saleh and Mr Samsuri Samsudin for their help.

**Author Contributions:** Mohd Norizam Md Daud: Writing-original draft, Validation, Investigation, Formal analysis, Data curation, Conceptualization. Amin Aadenan: Investigation, Conceptualization. Mohd Adib Ibrahim: Writing-review & editing, Najah Syahirah Mohd Nor: Writing-review & editing, Formal analysis. Mohd Asri Mat Teridi: Supervision, Writing-review & editing.

**Funding:** This research was funded by Geran Universiti Penyelidikan (GUP-2020-073) of Universiti Kebangsaan Malaysia (UKM) for this article.

## **Conflicts of interest**

The authors declare no conflict of interest

### References

Akila, B. S., Vaithinathan, K., Balaganapathi, T., Vinoth, S., & Thilakan, P. (2017). Investigations on the correlation between surface texturing histogram and the spectral reflectance of (100) Crystalline Silicon Substrate textured using anisotropic etching. Sensors and Actuators, A: Physical, 263, 445–450. https://doi.org/10.1016/j.sna.2017.06.021

- Al-Husseini, A. M., & Lahlouh, B. (2019). Influence of pyramid size on reflectivity of silicon surfaces textured using an alkaline etchant. *Bulletin of Materials Science*, 42(4). https://doi.org/10.1007/s12034-019-1848-7

- Bakhshi, S., Zin, N., Ali, H., Wilson, M., Chanda, D., Davis, K. O., & Schoenfeld, W. V. (2018). Simple and versatile UV-ozone oxide for silicon solar cell applications. *Solar Energy Materials and Solar Cells*, 185, 505–510. https://doi.org/10.1016/j.solmat.2018.06.006

- Bolon, D. A., & Kunz, C. O. (1972). Ultraviolet depolymerization of photoresist polymers. *Polymer Engineering & Science*, 12(2), 109– 111. https://doi.org/10.1002/pen.760120206

- Chen, G. (1999). The Applications of DI-O3 Water on Wafer Surface Preparation. *International Conference on Wafer Rinsing*. http://www.akrionsystems.com/wp-content/uploads/2012/01/The-Application-of-DIO3-Water-on-Wafer-Surface-Preparation.pdf

- Chen, W., Dhayagude, T., Chaparala, P., Demirlioglu, E., Shenasa, M., Bearda, T., Arnauts, S., & Meuris, M. (1997). RCA and IMEC/SC2 clean: Metallic immunity and gate oxide integrity. Materials Research Society Symposium - Proceedings, 477, 225– 232. https://doi.org/10.1557/proc-477-225

- Chu, C. L., Lu, T. Y., & Fuh, Y. K. (2020). The suitability of ultrasonic and megasonic cleaning of nanoscale patterns in ammonia hydroxide solutions for particle removal and feature damage. Semiconductor Science and Technology, 35(4). https://doi.org/10.1088/1361-6641/ab675d

- Chu, M., Khokhar, M. Q., Kim, Y., Quddamah Khokhar, M., Yousuf, H., Fan, X., Han, S., Dhungel, S. K., & Yi, J. (2024). Review of the Silicon Oxide and Polysilicon Layer as the Passivated Contacts for TOPCon Solar Cells. https://doi.org/10.4313/JKEM.2023.36.3.4

- Chuchvaga, N. A., Kisiyakova, N. M., Tokmoldin, N. S., Rakymetov, B. A., & Serikkanov, A. S. (2020). Problems Arising from Using KOH–IPA Etchant to Texture Silicon Wafers. *Technical Physics*, 65(10), 1685–1689. https://doi.org/10.1134/S1063784220100047

- Das, M., & Sarkar, D. (2016). Morphological and optical properties of n-type porous silicon: Effect of etching current density. *Bulletin of Materials Science*, 39(7), 1671–1676. https://doi.org/10.1007/s12034-016-1332-6

- Epelle, E. I., Macfarlane, A., Cusack, M., Burns, A., Okolie, J. A., Mackay, W., Rateb, M., & Yaseen, M. (2023). Ozone application in different industries: A review of recent developments. In Chemical Engineering Journal, 454. https://doi.org/10.1016/j.cej.2022.140188

- Fang, H., Li, X., Song, S., Xu, Y., & Zhu, J. (2008). Fabrication of slantingly-aligned silicon nanowire arrays for solar cell applications. *Nanotechnology*, 19(25). https://doi.org/10.1088/0957-4484/19/25/255703

- Fashina, A., Adama, K., Abdullah, L., Ani, C., Oyewole, O., Asare, J., & Anye, V. (2018). Atomic force microscopy analysis of alkali textured silicon substrates for solar cell applications. *International Journal of Physical Research*, 6(1), 13–17. https://doi.org/10.14419/ijpr.v6i1.8795

- Fink, C. K., Nakamura, K., Ichimura, S., & Jenkins, S. J. (2009). Silicon oxidation by ozone. *Journal of Physics Condensed Matter*, 21(18). https://doi.org/10.1088/0953-8984/21/18/183001

- Fu, T., Zhang, Y., Chen, L., Shen, F., & Zhu, J. (2024). Micromorphology evolution, growth mechanism, and oxidation behaviour of the silicon-rich MoSi2 coating at 1200 °C in air. *Journal of Materials Research and Technology*, 29, 491–503. https://doi.org/10.1016/j.jmrt.2024.01.112

- Gao, M. (2021). UV-Ozone Oxide Treatments for High-Efficiency Silicon Photovoltaic Devices. https://stars.library.ucf.edu/etd2020/504

- Garnett, E., & Yang, P. (2010). Light trapping in silicon nanowire solar cells. *Nano Letters*, 10(3), 1082–1087. https://doi.org/10.1021/nl100161z

- Jiang, Y., Zhang, X., Wang, F., & Zhao, Y. (2015). Optimization of a silicon wafer texturing process by modifying the texturing temperature for heterojunction solar cell applications. *RSC Advances*, 5(85), 69629–69635. https://doi.org/10.1039/c5ra09739h

- Ju, M., Balaji, N., Park, C., Thanh Nguyen, H. T., Cui, J., Oh, D., Jeon, M., Kang, J., Shim, G., & Yi, J. (2016). The effect of small pyramid texturing on the enhanced passivation and efficiency of single c-Si solar cells. *RSC Advances*, 6(55), 49831–49838. https://doi.org/10.1039/c6ra05321a

- Jun, M. C., Kim, Y. S., Han, M. K., Kim, J. W., & Kim, K. B. (1995).

Polycrystalline silicon oxidation method improving surface roughness at the oxide/polycrystalline silicon interface. *Applied Physics Letters*, 2206. https://doi.org/10.1063/1.113948

- K, A. K., & O, E. J. (2023). Experimental Analysis of Anisotropic Surface Texturing Process of Crystalline Silicon Wafers. *Journal of Materials Engineering, Structures and Computation*, 2(1), 2023–2024. https://doi.org/10.5281/zenodo.7759299

- Kart, D., Gürel, D. B., Kayaardi, S., & Gurel, D. B. (2018). Cold Plasma and Ultrasound Applications in Cleaning of Food Contact Surfaces. *International Journal of Scientific and Technological Research*, 4(8). https://www.iiste.org/Journals/index.php/JSTR/article/vie w/44469

- Kegel, J., Angermann, H., Stürzebecher, U., & Stegemann, B. (2013). IPA-free texturization of n-type Si wafers: Correlation of optical, electronic and morphological surface properties. *Energy Procedia*, 38, 833–842. https://doi.org/10.1016/j.egypro.2013.07.353

- Kern, W., & Puotinen, D. A. (1970). Cleaning Solutions Based on Hydrogen Peroxide for Use in Silicon Semiconductor Technology. RCA Review, A Tehcnical Journal ,31. https://garfield.library.upenn.edu/classics1983/A1983QD902 00001.pdf

- Khanna, A., Basu, P. K., Filipovic, A., Shanmugam, V., Schmiga, C., Aberle, A. G., & Mueller, T. (2015). Influence of random pyramid surface texture on silver screen-printed contact formation for monocrystalline silicon wafer solar cells. Solar Energy Materials and Solar Cells, 132, 589–596. https://doi.org/10.1016/j.solmat.2014.10.018

- Li, S., Li, Z., Wan, X., & Chen, Y. (2023). Recent progress in flexible organic solar cells. eScience, 3(1). https://doi.org/10.1016/j.esci.2022.10.010

- Menna, P., Di Francia, G., & Ferrara, V. La. (1995). Porous silicon in solar cells: A review and a description of its application as an AR coating. Solar Energy Materials and Solar Cells, 37. https://doi.org/10.1016/0927-0248(94)00193-6

- Moldovan, A., Birmann, K., Rentsch, J., Zimmer, M., Gitte, T., & Fittkau, J. (2013). Combined ozone/HF/HCl based cleaning and adjusted emitter etch-back for silicon solar cells. *Solid State Phenomena*, 195, 305–309. https://doi.org/10.4028/www.scientific.net/SSP.195.305

- Montesdeoca-Santana., A., Orive, A. G., Creus, A. H., González-Díaz, B., Borchert, D., & Guerrero-Lemus, R. (2013). Microscopy analysis of pyramid formation evolution with ultra-low concentrated Na2CO3/NaHCO3 Solution on (100) Si for Solar Cell Application. *Microscopy and Microanalysis*, 19(2), 285–292. https://doi.org/10.1017/S1431927612014237

- Neutens, P., Rutowska, M., Van Roy, W., Jansen, R., Buja, F., & Van Dorpe, P. (2018). Influence of UV Light on PECVD Silicon Nitride Waveguide Propagation Loss. *IEEE International Conference on Group IV Photonics GFP*, 2018-Augus, 121–122. https://doi.org/10.1109/GROUP4.2018.8478749

- Norizam, M., Daud, M., Firdaus, M., Noh, M., Arzaee, N. A., Aadenan, A., Hakim, D., Hisham, B., Athir, M., Anuar, M., Ibrahim, M. A., Sepeai, S., Asri, M., & Teridi, M. (2024). Electrochemical induced morphological formation and optical properties of ptype silicon wafer. *Bull Mater Sci* 47, 268. https://doi.org/10.1007/s12034-024-03349-3

- Oni, A. M., Mohsin, A. S. M., Rahman, M. M., & Hossain Bhuian, M. B. (2024). A comprehensive evaluation of solar cell technologies, associated loss mechanisms, and efficiency enhancement strategies for photovoltaic cells. In *Energy Reports* (Vol. 11, pp. 3345–3366). Elsevier Ltd. https://doi.org/10.1016/j.egyr.2024.03.007

- Özçam, A. E., Efimenko, K., & Genzer, J. (2014). Effect of ultraviolet/ozone treatment on the surface and bulk properties of poly(dimethyl siloxane) and poly(vinylmethyl siloxane)

- networks. *Polymer*, *55*(14), 3107–3119. https://doi.org/10.1016/j.polymer.2014.05.027

- Panagoda, L. P. S. S., Sandeepa, R. A. H. T., Perera, W. A. V. T., Sandunika, D. M. I., Siriwardhana, S. M. G. T., Alwis, M. K. S. D., & Dilka, S. H. S. (2023). Advancements In Photovoltaic (Pv) Technology for Solar Energy Generation. *J. Res. Technol. Eng* 4(3). https://www.researchgate.net/publication/372364724

- Park, H., Ju, M., Khokhar, M. Q., Cho, E. C., Kim, Y., Cho, Y., & Yi, J. (2020). Surface Modifications for Light Trapping in Silicon Heterojunction Solar Cells: A Brief Review. *Transactions on Electrical and Electronic Materials*, 21(4), 349–354. https://doi.org/10.1007/s42341-020-00203-1

- Park, H., Kwon, S., Lee, J. S., Lim, H. J., Yoon, S., & Kim, D. (2009). Improvement on surface texturing of single crystalline silicon for solar cells by saw-damage etching using an acidic solution. *Solar Energy Materials and Solar Cells*, 93(10), 1773–1778. https://doi.org/10.1016/j.solmat.2009.06.012

- Raji, M., Venkatachalam, K., Manikkam, S., & Perumalsamy, R. (2022). Surface Texturing of the Multi-Crystalline Silicon Wafers Using Novel Non-Toxic Chemical Composition. *Silicon*, *14*(15), 9987–9995. https://doi.org/10.1007/s12633-022-01759-8

- Ruzyllo, J., Pintchovski, F., Price, J. B., & Tobin, P. J. (1990). The Evolution of Silicon Wafer Cleaning Technology. *J. Electrochem. Soc*, 137, 1887–1892. https://doi.org/10.1149/1.2086825

- Zhang, Y., Wang, B., Li, X., Gao, Z., Zhou, Y., Li, M., Zhang, D., Tao, K., Jiang, S., Ge, H., Xiao, S., & Jia, R. (2021). A novel additive for rapid and uniform texturing on high-efficiency monocrystalline silicon solar cells. *Solar Energy Materials and Solar Cells*, 222. https://doi.org/10.1016/j.solmat.2020.110947

- Zou, S., Xu, L., Wu, C., Ding, J., Zhu, L., Sun, H., Ye, X., Wang, X., Zhang, X., & Su, X. (2021). Metal-catalyzed chemical etching using DIO3 as a hole injection agent for efficient submicron-textured multicrystalline silicon solar cells. Solar Energy Materials and Solar Cells, 227. https://doi.org/10.1016/j.solmat.2021.111104

© 2025. The Author(s). This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution-ShareAlike 4.0 (CC BY-SA) International License (http://creativecommons.org/licenses/by-sa/4.0/)